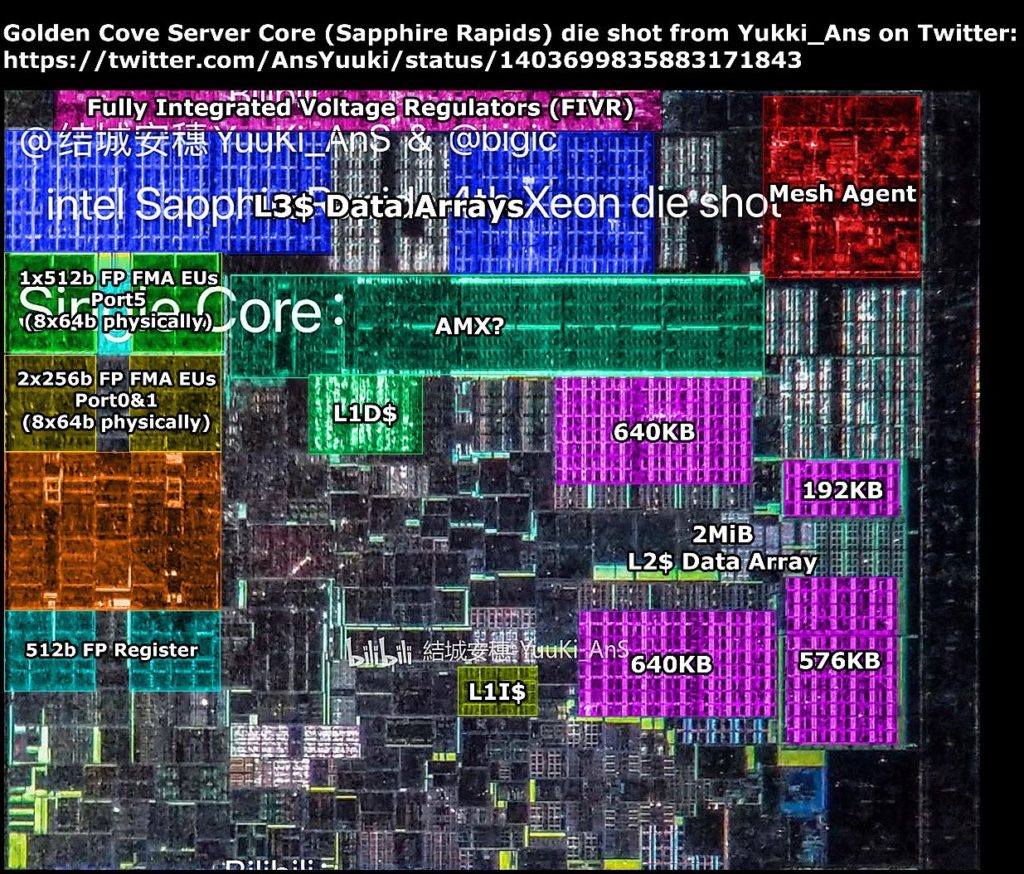

Una mirada a la arquitectura central Golden Cove de Intel a través de Sapphire Rapids-SP Die Shot: 2 MB L2 y unidades AMX

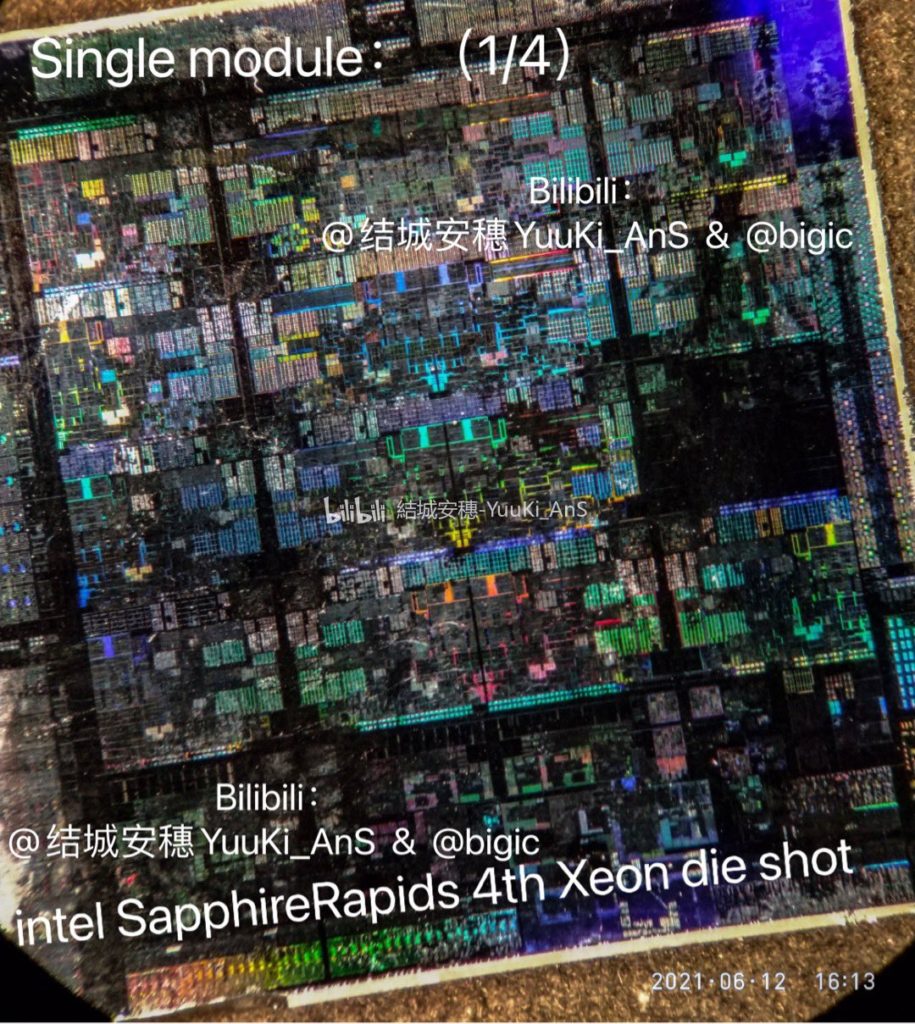

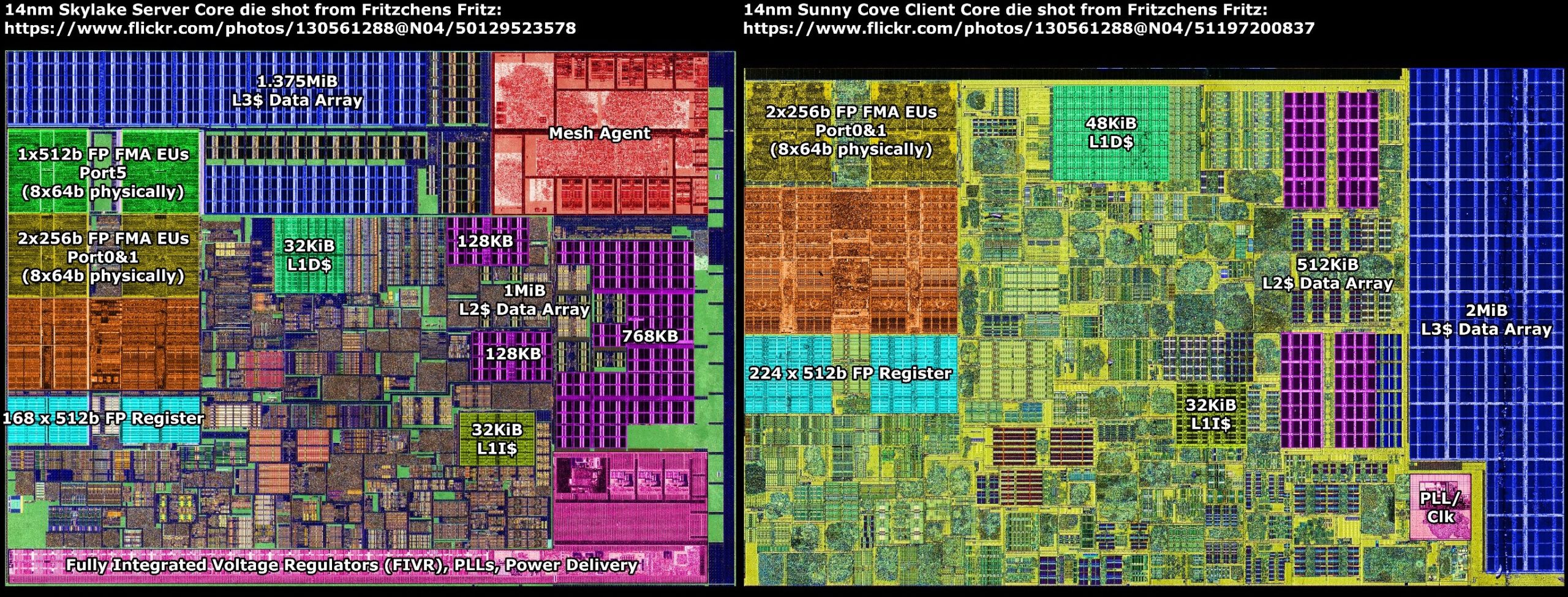

Algunas primeras tomas del próximo Sapphire Rapids-SP de Intel han revelado la arquitectura central de Golden Cove, que se aprovechará en las líneas de procesadores de próxima generación de la compañía. En cuanto al núcleo, parece ser más o menos similar a Sunny Cove y Skylake, con una unidad de ejecución FP512 (para AVX512) y dos unidades FP256, y aproximadamente la misma cantidad de registros que la primera.

La caché L2 ha crecido significativamente, pasando de solo 512 KB (por núcleo) en Sunny Cove a aproximadamente 2 MB en Golden Cove. La caché L1I también parece haber crecido a 48 KB en el último de 32 KB en el primero. La adición más notable es la inclusión de AMX (unidades de matriz) en Golden Cove, que debería ayudar a mejorar las instrucciones avanzadas de Tensor y, por lo tanto, acelerar el entrenamiento de la red neuronal.

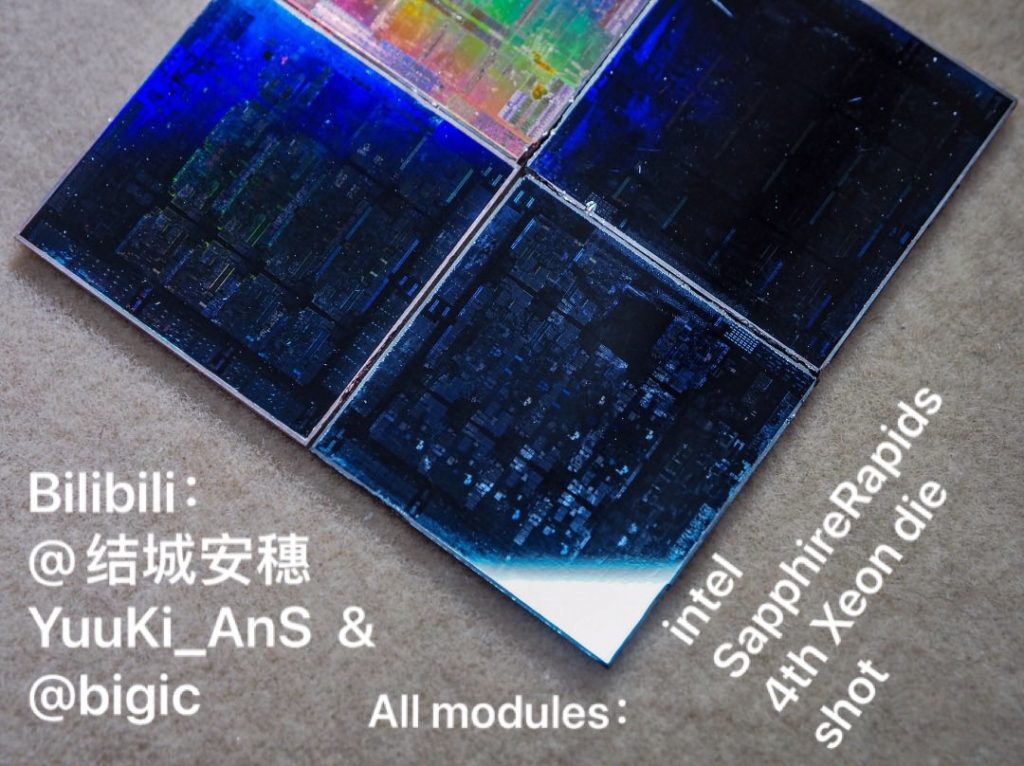

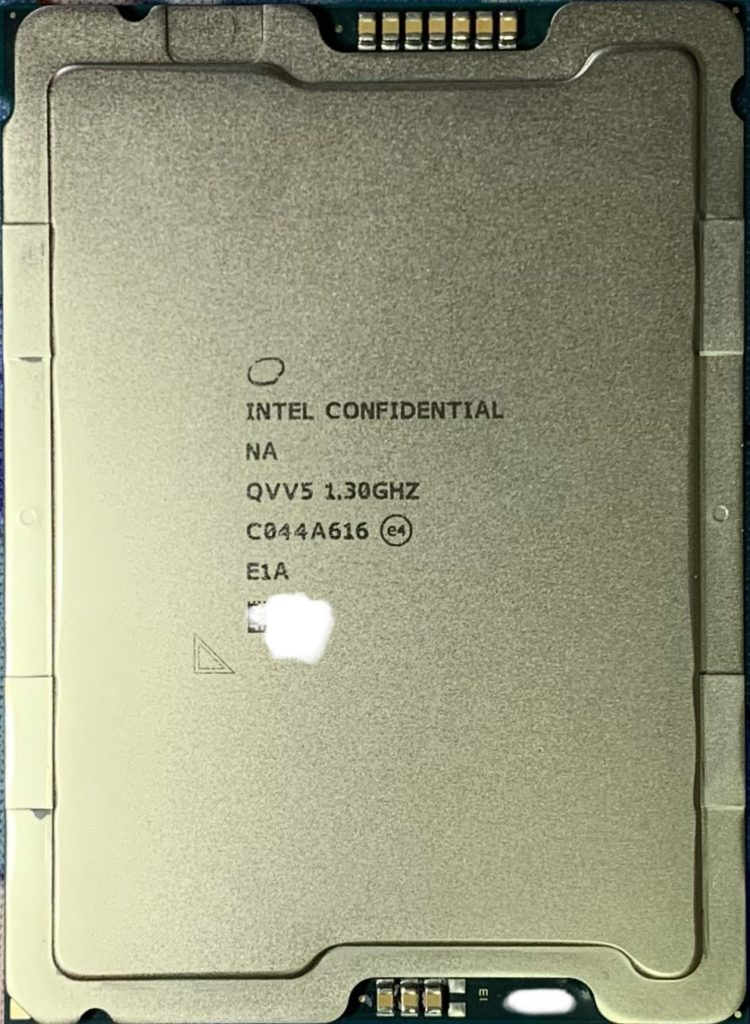

El resto de los tiros de dado no revelan mucho sobre el SKU. El soporte para HBM2 en matriz ya es un hecho conocido desde hace un tiempo, así como el hecho de que SPR contará con un diseño de chiplet con hasta cuatro mosaicos y un recuento total de núcleos de 56-60. Un pequeño detalle es nuevo. Parece que los procesadores escalables Xeon de cuarta generación también contarán con un FPGA Altera, pero no está claro cuál será su función.

La publicación Una mirada a la arquitectura central Golden Cove de Intel a través de Sapphire Rapids-SP Die Shot: 2MB L2 y AMX Units apareció primero en Hardware Times.