Intel Big Core vs Small Core: diferencia entre las arquitecturas Tremont / Gracemont y Skylake Core

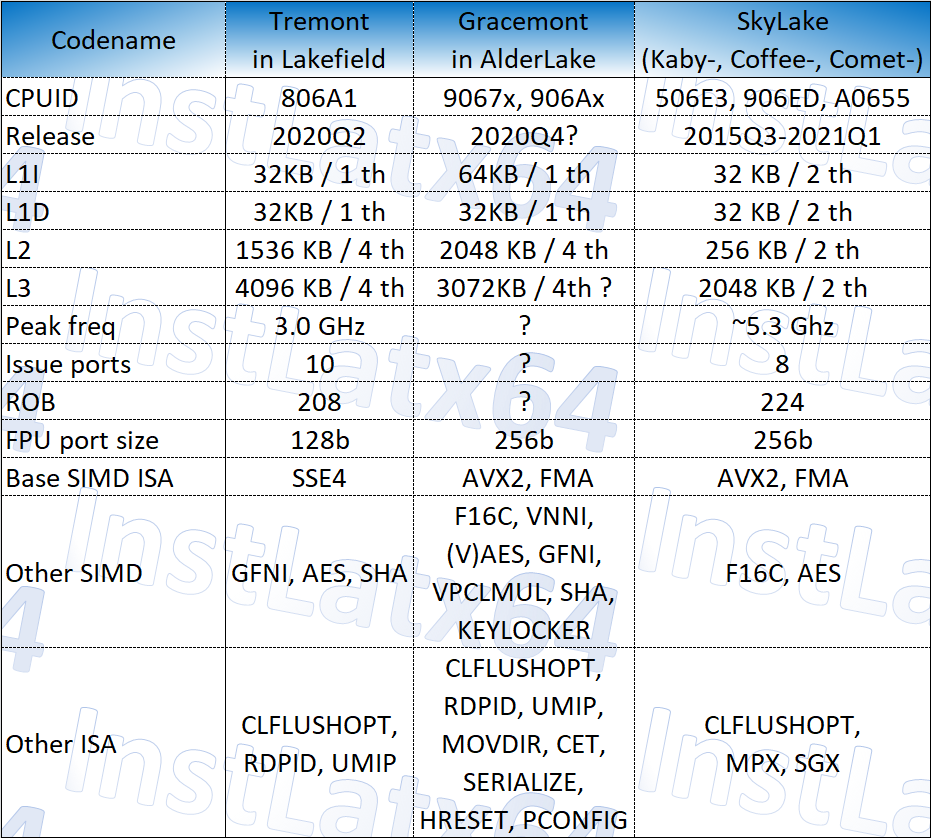

Con Alder Lake, Intel, por primera vez, se está moviendo hacia una arquitectura de núcleo híbrido en todo su conjunto de productos, desde el 9-15 W U15 hasta la línea de escritorio “S” de 125 W. Alder Lake combinará dos arquitecturas centrales diferentes, a saber, Golden Cove y Gracemont (ambos ESF de 10 nm) para un enfoque más flexible del rendimiento y la eficiencia energética. Si bien esto puede parecer una solución simple para hacer que los procesadores sean más eficientes energéticamente, la realidad es más complicada. El programador del sistema operativo debería poder distinguir inteligentemente entre los dos y decidir qué cargas de trabajo son las más adecuadas para cada clúster central. Además, las ISA compatibles con las dos arquitecturas no son idénticas. Los núcleos Atom “pequeños” no admiten todas las instrucciones admitidas por el núcleo “grande”, siendo los más notables AVX2 y FMA con Tremont. Como tal, cuando se ejecuta una aplicación que aprovecha este tipo de instrucciones en Tremont, serán un poco más lentas que en Skylake.

En esta publicación, me gustaría echar un vistazo al predecesor del próximo núcleo Gracemont (que será el núcleo de bajo consumo en Alder Lake) y compararlo con Skylake, que básicamente se ha convertido en una arquitectura “de facto” (no literalmente, fíjate) durante los últimos 4-5 años. Como tal, si GC es capaz de ofrecer un rendimiento comparable al de Skylake o superarlo, será difícil considerarlo como una alternativa de bajo consumo. En cambio, estos núcleos deberían funcionar de manera similar a los procesadores -Lake más antiguos en la mayoría de las cargas de trabajo, incluso cuando los núcleos Golden Cove están inactivos. Echaremos un vistazo a las ISA, el front-end, el back-end y las frecuencias de las dos arquitecturas centrales y veremos cómo ha madurado la arquitectura Atom a lo largo de los años.

Intel Big Core vs Small Core: Tremont vs Skylake, Frontend y Backend

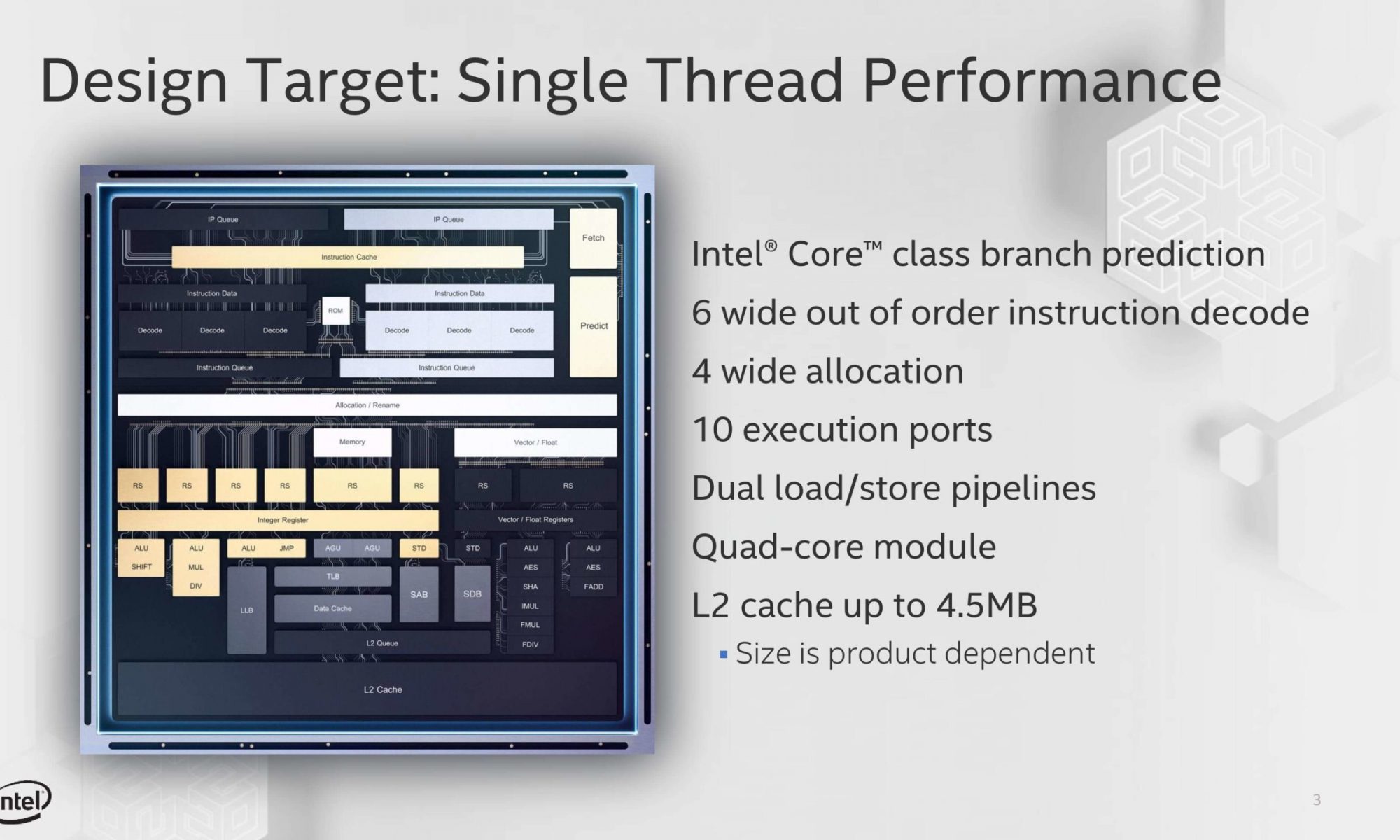

Tenga en cuenta que si bien comparar Gracemont (una arquitectura aún inédita) con un diseño de 5 años no es del todo justo, vale la pena señalar que, en este momento, el 75% o más de la base total de usuarios de Blue todavía está usando alguna forma de Skylake. Como todavía no tenemos el diagrama de bloques de Gracemont, usaremos Tremont como referencia con algunas especulaciones aquí y allá. Comenzando con el predictor de sucursales, Tremont tiene un predictor de clase Core que funciona de manera muy similar a Skylake con algunos compromisos con el tamaño de la tabla de predicción. Gracemont debería estar aún más cerca, si no mejor, que Skylake en términos de BP. El hecho de que el último usa un nodo de 14nm mientras que el primero se basa en el más nuevo de 10nm El proceso debería haber proporcionado el área de matriz requerida.

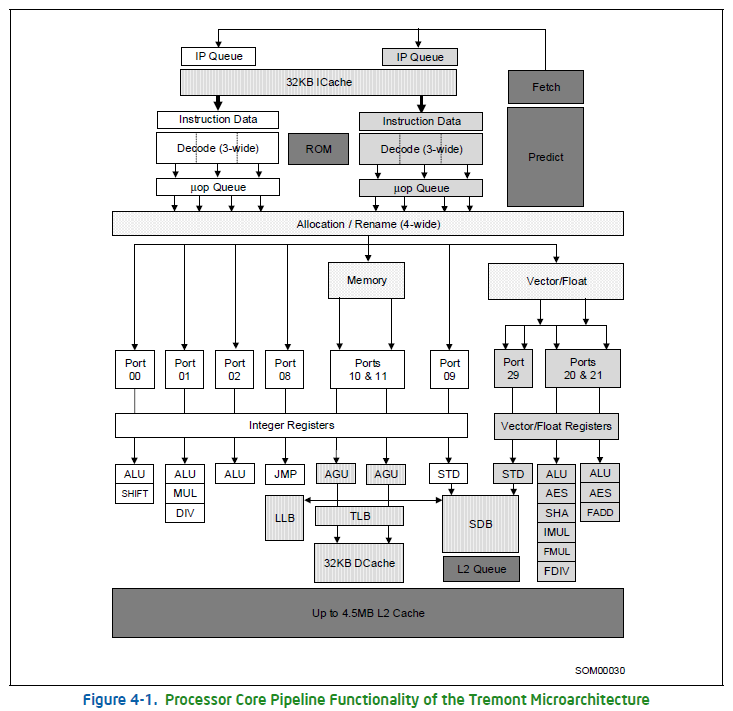

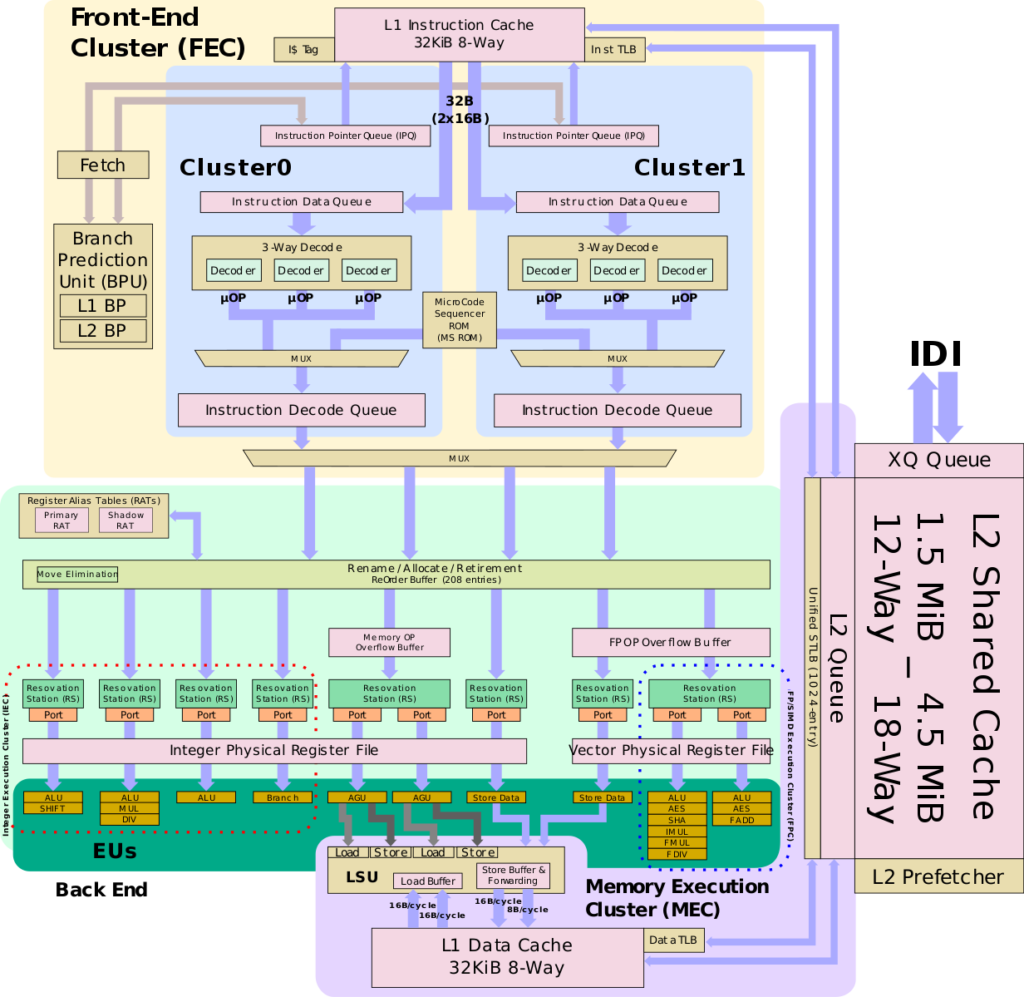

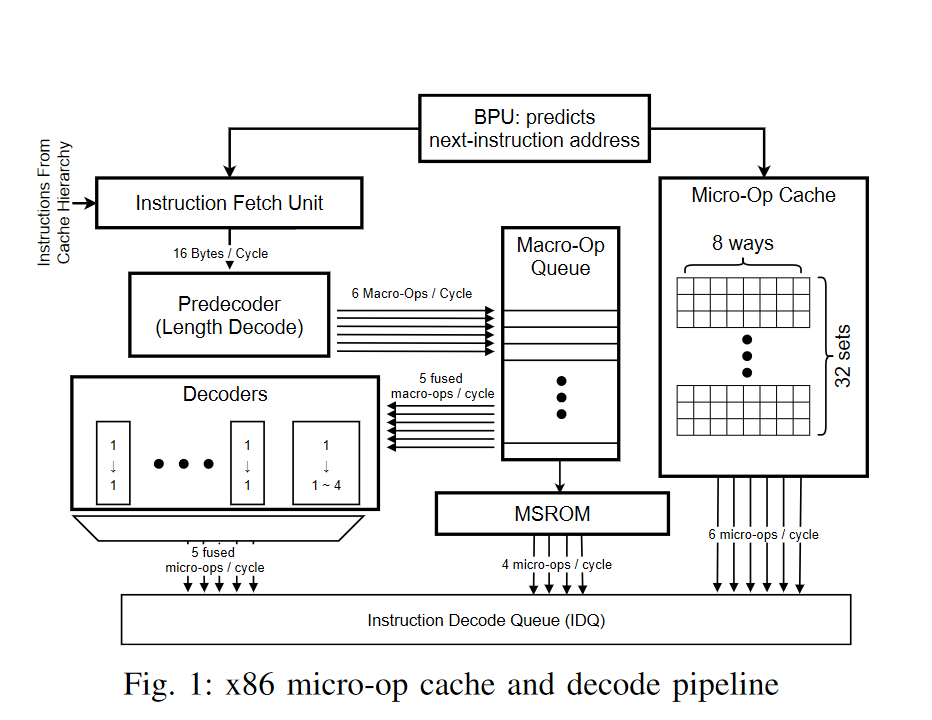

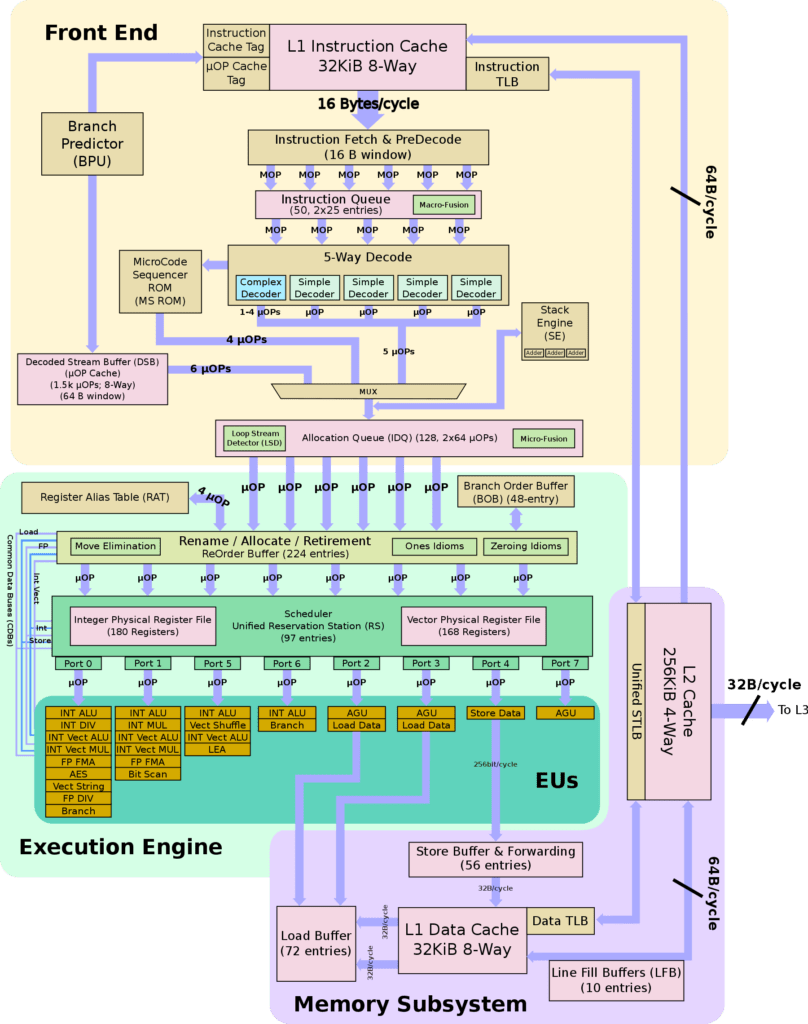

Tremont tiene un decodificador de instrucciones muy interesante. Cuenta con dos decodificadores de 3 anchos, cada uno de los cuales es alimentado por un flujo separado de instrucciones (16Bx2) de la caché L1I. A diferencia de Skylake (y Sunny Cove), Tremont no tiene una etapa de pre-decodificación separada (¿o macrofusión?). Si bien esto no debería importar mucho, la falta de un caché de operaciones debería marcar una diferencia notable. Skylake tiene cuatro decodificadores 1: 1 y un decodificador complejo 1: 4 además de un caché de microoperaciones capaz de suministrar hasta 6 microoperaciones por ciclo. Tremont esencialmente tiene solo un decodificador de tres anchos.

La principal ventaja de un decodificador dual es que los dos se alimentan por separado y, como tal, cuando se trabaja con dos predicciones de rama diferentes, se pueden realizar ambas simultáneamente. Sin embargo, cuando no hay una rama (raro, pero sucede), uno de los decodificadores se apaga para ahorrar energía. Si bien el documento técnico de Intel dice lo contrario, la falta de un micro-op-cache debería tener un impacto notable en las capacidades del front-end. En general, Tremont (y, por lo tanto, Gracemont) tiene un frontend bien construido, capaz de mantener el backend bien alimentado en la mayoría de los escenarios.

[It’s possible that we will see one with Gracemont as Sunny Cove boosted its capacity by 50% compared to Skylake. Even with older architectures such as Ivy and Sandybridge, the op-cache boosts throughput by 20-25%. This has only increased over generations and is highly unlikely that Tremont or Gracemont would perform worse without one. AMD uses a standard x86 decoder capable of decoding four macro-instructions per cycle, with the micro-op cache delivering up to eight cached instructions, making it much more effective than the standard decode pipeline. It’s for this reason that u-op caches of most modern processors have a high hit rate of over 75% in most cases..]Otra ventaja que tiene Skylake es que puede fusionar múltiples microoperaciones similares en una instrucción única que luego se puede procesar de una vez. Tremont parece carecer de esto, y es poco probable que lo veamos parcheado en Gracemont.

Las partes más notables del backend incluyen los búferes de reorden, las unidades de ejecución y los archivos de registro. Tremont tiene un ROB bastante grande capaz de contener 208 instrucciones, frente a 224 en Skylake y 352 en Sunny Cove. La principal diferencia entre los núcleos grandes y pequeños de Intel aquí es con respecto a la estación de reserva (programador de instrucciones) donde las microoperaciones esperan la ejecución o el uso para el cambio de nombre del registro. Mientras que Skylake y Sunny Cove tienen un único RS (grande) que contiene hasta 97 entradas, Tremont (y probablemente GM) tienen estaciones individuales para cada puerto. Las dos UE vectoriales tienen una reserva compartida y también otro par de unidades de generación de direcciones (AGU) para dos almacenes / cargas de 16 bytes, o uno de cada uno.

Skylake puede hacer dos cargas y una tienda por ciclo, mientras que cuatro puertos están dedicados a ellos. Además, mientras que Tremont tiene puertos separados para la ejecución de números enteros y de punto flotante, Skylake y Sunny Cove comparten puertos comunes para ambos. La otra diferencia es con respecto a las ALU mismas. Si bien Skylake tiene varias unidades vectoriales de 256 bits, Tremont está limitado a EU de 128b de ancho, aunque es casi seguro que se espera que Gracemont las unidades 256b Admite AVX2 y FMA nativos.

Caché L1 y L2: Tremont / Gracemont vs Skylake

Tremont tiene un TLB L2 de 1024 entradas, mientras que Sunny Cove puede contener hasta 2048. En comparación, Skylake podría contener hasta 1,536 entradas y Zen 3 está limitado a solo 512. Al igual que Sunny Cove, tanto Zen 2 como Zen 3 tienen un caché L1I de 32 KB de 8 vías, con el búfer de destino de rama L1 duplicado a 1,024 entradas (512 en Zen 2) en Zen 3, L0 sin cambios en 16 y L2 BTB ligeramente más ancho en 6.5K (6K en Zen 2).

Gracemont

Tremont

Goldmont +

Goldmont

Sunny Cove

Skylake

Proceso

FSE de 10 nm

10 nm +

14 nm ++

14 nm

10 nm +

14 nm ++

Descodificar

4-6 vías?

2 × 3 vías

3 vías

3 vías

5 vías

5 vías

Asignar

4 de ancho?

4 de ancho

4 de ancho

3 de ancho

10 de ancho

8 de ancho

Instrucción L1

64 KB

16 vías

32 KB

8 vías

32 KB

8 vías

32 KB

8 vías

32 KB

8 vías

32 KB

8 vías

Datos L1

32 KB

8 vías

32 KB

8 vías

24 KB

6 vías

24 KB

6 vías

48 KB

12 vías

32 KB

8 vías

Latencia L1

3 ciclos

3 ciclos

3 ciclos

3 ciclos

5 ciclos

4 ciclos

Caché L2

1,5 MB

1,5

12-18 vías

1,0 MB

16 vías

0,5-1,0 MB

16 vías

512 KB

8 vías

256 KB

4 maneras

Latencia L2

17 ciclos?

17 ciclos

19 ciclos

17 ciclos

13 ciclos

12 ciclos

Tremont tiene un tamaño de caché L1D de 32 KB con asociatividad de 8 vías, y también lo es la caché L1I. Se espera que Gracemont amplíe este último a 64 KB / núcleo con asociatividad de 16 vías. Skylake también tiene el mismo tamaño de caché L1 que Tremont, aunque con una latencia más alta de 4 ciclos. Sunny Cove tiene una caché L1D de 12 vías de 48 KB más grande, pero una latencia aún mayor de 5 ciclos. Tremont y Gracemont deberían tener una latencia de 3 ciclos relativamente más baja.

Tremont tiene una caché L2 de hasta 4 MB para un conjunto de cuatro núcleos (un módulo), y cada núcleo tiene acceso a aproximadamente 1,5 MB de él. Esto es un poco más que Skylake e incluso Sunny Cove, pero una mayor capacidad también significa una mayor latencia.

Instrucciones y frecuencias: Tremont / Gracemont vs Skylake

Finalmente, está la cuestión de las instrucciones admitidas en las dos arquitecturas diferentes. Si bien Tremont carece de soporte para AVX2 o FMA a nivel nativo, se espera que Gracemont admita ambos, poniéndolo más o menos a la par con Skylake en términos de ISA de uso común. Todavía hay algunas instrucciones que faltarán en los Monts, como AVX512, SGX y AMX, pero eso debería ser de poca importancia para el usuario promedio.

Al final del día, lo que eventualmente frenará los núcleos Gracemont en comparación con Skylake son las frecuencias operativas. Si bien los diseños más nuevos de Skylake alcanzan fácilmente los 4.5-5.0GHz en todos los núcleos, se espera que el primero se mantenga por debajo de la marca de 3.5GHz. Esto significa que a pesar de la paridad arquitectónica cercana, debería haber un delta notable entre los dos. El hecho de que Tremont tenga un reloj base de 1.5-2GHz debería reiterarlo aún más. Sin embargo, estos son núcleos de baja potencia y deberían operar en este rango de frecuencia, o su propósito principal se perdería más o menos. Para responder a la pregunta original, sí, Gracemont debería ser casi tan capaz como Skylake, pero se puede considerar como un núcleo Skylake de bajo consumo que se ejecuta en modo de ahorro de energía, con un notable delta de rendimiento entre los dos.

Lectura relacionada: